Back باور5 Arabic POWER5 Spanish POWER5 French POWER5 Hungarian POWER5 Italian POWER5 Japanese POWER5 Korean POWER5 Dutch POWER5 NB POWER5 Portuguese

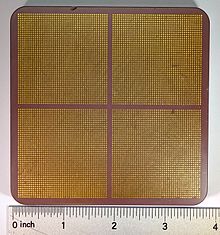

POWER5 MCM | |

| General information | |

|---|---|

| Launched | 2004 |

| Designed by | IBM |

| Performance | |

| Max. CPU clock rate | 1.5 GHz to 2.3 GHz |

| Cache | |

| L1 cache | 32+32 KB/core |

| L2 cache | 1.875 MB/chip |

| L3 cache | 36 MB/chip (off-chip) |

| Architecture and classification | |

| Technology node | 130 nm to 90 nm |

| Instruction set | PowerPC 2.02 |

| Physical specifications | |

| Cores |

|

| History | |

| Predecessor | POWER4 |

| Successor | POWER6 |

| POWER, PowerPC, and Power ISA architectures |

|---|

| NXP (formerly Freescale and Motorola) |

| IBM |

|

| IBM/Nintendo |

| Other |

| Related links |

| Cancelled in gray, historic in italic |

The POWER5 is a microprocessor developed and fabricated by IBM. It is an improved version of the POWER4. The principal improvements are support for simultaneous multithreading (SMT) and an on-die memory controller. The POWER5 is a dual-core microprocessor, with each core supporting one physical thread and two logical threads, for a total of two physical threads and four logical threads.